- 您现在的位置:买卖IC网 > Sheet目录3878 > PIC18F2431T-I/ML (Microchip Technology)IC MCU FLASH 8KX16 28QFN

Micrel, Inc.

KSZ8842-PMQL/PMBL

October 2007

76

M9999-100207-1.5

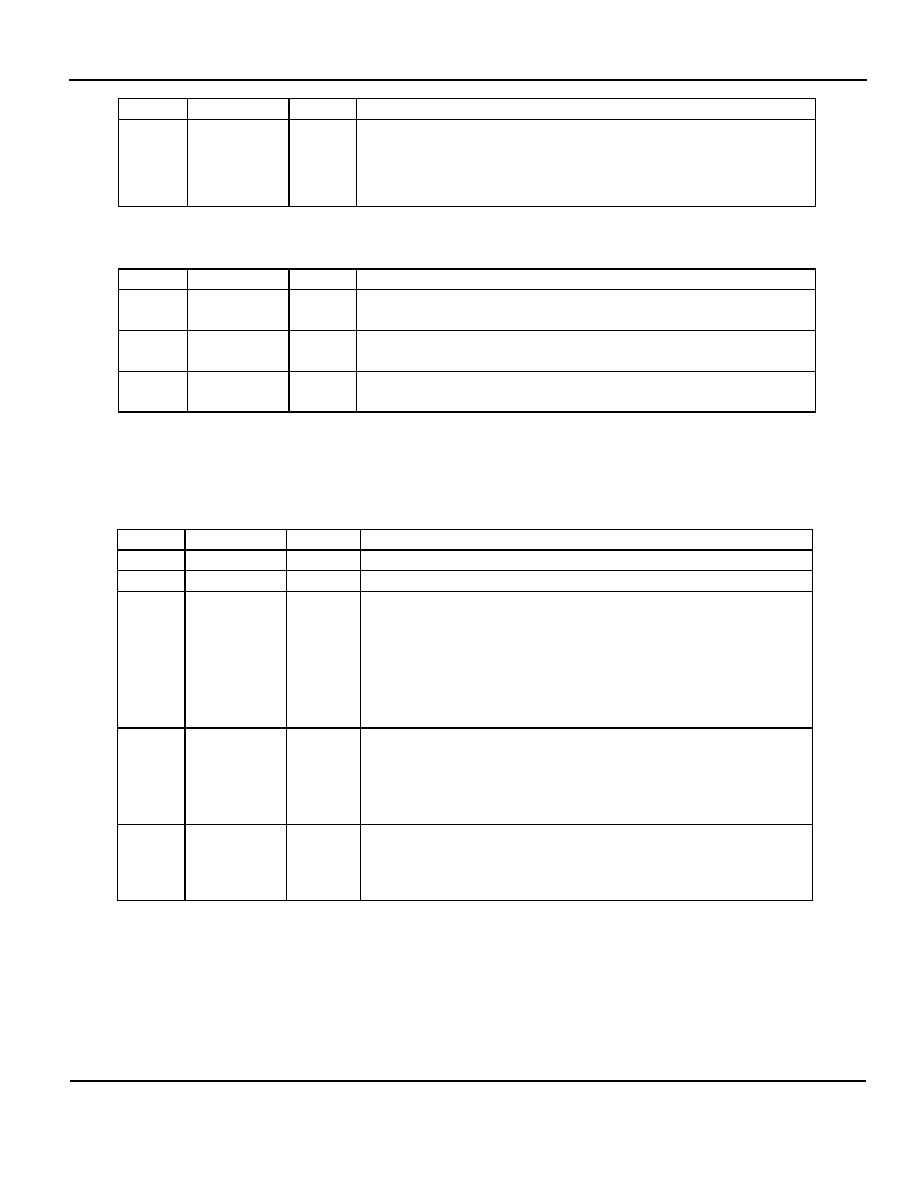

Bit

Default

R/W

Description

2 – 0

111

RW

Port VLAN membership

Define the port’s Port VLAN membership. Bit 2 stands for the host port,

bit 1 for port 2, and bit 0 for port 1. The Port can only communicate within

the membership. An ‘1’ includes a port in the membership; an ‘0’

excludes a port from the membership.

Port 1 VID Control Register (Offset 0x0504): P1VIDCR

This register contains the global per port control for the switch port 1 function.

Bit

Default

R/W

Description

15-13

000

RW

User Priority bits

Port 1 tag [15-13] for priority

12

0

RW

CFI bit

Port 1 tag [12] for CFI

11-0

0x001

RW

VID

Port 1 tag [11-0] for VID

Note: P1VIDCR serve two purposes:

(1) Associated with the ingress untagged packets, and used for egress tagging.

(2) Default VID for the ingress untagged or null-VID-tagged packets, and used for address look up.

Port 1 Control Register 3 (Offset 0x0506): P1CR3

This register contains the port 1 control register for the switch port 1 function.

Bit

Default

R/W

Description

15 – 5

00000000000

RO

Reserved

4

0

RW

Reserved

3:2

00

RW

Ingress Limit Mode.

These bits determine what kinds of frames are limited and counted

against Ingress limiting as follows:

00 = limit and count all frames

01 = limit and count Broadcast, Multicast, and flooded unicast frames

10 = limit and count Broadcast and Multicast frames only

11 = limit and count Broadcast frames only

1

0

RW

Count IFG bytes

1 = each frame’s minimum inter frame gap

(IFG) bytes (12 per frame) are included in Ingress and Egress rate

limiting calculations.

0 = IFG bytes are not counted

0

RW

Count Preamble bytes

1 = each frame’s preamble bytes (8 per frame) are included in Ingress

and Egress rate limiting calculations.

0 = preamble bytes are not counted

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16LF1938-I/SO

IC MCU 8BIT FLASH 28SOIC

PIC16F639-E/SO

IC MCU FLASH 2KX14 20SOIC

PIC24F08KL402-I/SS

IC MCU 16BIT 8KB FLASH 28-SSOP

PIC16F1936-I/MV

IC MCU 8BIT 14KB FLASH 28UQFN

PIC16LF724-I/PT

IC PIC MCU FLASH 7KB 44-TQFP

PIC16F724-I/MV

MCU 7KB FLASH PROGRAM 40-UQFN

PIC16LF724-I/MV

MCU PIC 7KB FLASH XLP 40-UQFN

PIC18F2331T-I/SO

IC MCU FLASH 4KX16 28SOIC

相关代理商/技术参数

PIC18F2431T-I/MM

功能描述:8位微控制器 -MCU 16 KB FL 768 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2431T-I/SO

功能描述:8位微控制器 -MCU 16KB 768 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2439-E/SO

功能描述:8位微控制器 -MCU 16KB 768 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2439-E/SP

功能描述:8位微控制器 -MCU 16KB 768 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2439-I/SO

功能描述:8位微控制器 -MCU 12KB 640 RAM 21 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2439-I/SP

功能描述:8位微控制器 -MCU 12KB 640 RAM 21 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F2439-I/SP

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F2439 SDIL28

PIC18F2439T-E/SO

功能描述:8位微控制器 -MCU MCU CMOS 28 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT